Точность измерения всех токовых данных составила около 2%, а пороговых — около 0.5%. Контроль точности осуществлялся путем 6-кратного повторения каждого из трех измерительных наборов.

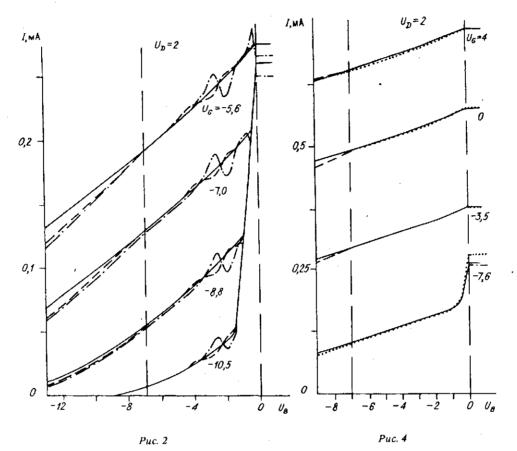

Данные для рис. 4—6 в третьем наборе содержат все виды вольт-амперных характеристик (сплошной линией отмечены экспериментальные вольт-амперные характеристики, точками — характеристики, смоделированные с помощью интерполяционного транзистора, штрихпунктиром — характеристики подогнанной под эксперимент малоразмерной аналитической модели, а штриховой линией — характеристики подогнанной большеразмерной модели [8]). Для интерполяционного транзистора была выбрана сетка  $9 \times 3 \times 8 = 216$  узлов.

Заключение. Разработанный алгоритм позволил создать относительно компактные по числу узлов данных и занимаемой оперативной памяти интерполяционные модели. Решение проблемы монотонности значительно упростило процедуру выбора сеток, подчинив ее лишь одной цели — точности интерполяции. Алгоритм внедрен в пяти типах интерполяционных моделей с индуцированным и встроенным каналами, которые в сочетании с автоматизацией измерения параметров хорошо зарекомендовали себя при проведении точных расчетов схем. По усредненной ошибке они превосходят малоразмерные аналитические модели более чем в 10 раз и обеспечивают точность относительной ошибки интерполяции на уровне 3 % в диапазоне токов, отличающихся на четыре порядка.

Автор выражает благодарность В. Л. Мирошниченко за ценную информацию при обсуждении проблем монотонности.

#### СПИСОК ЛИТЕРАТУРЫ

- Coughran W. M. et al. Variation diminishing splines in simulation // SIAM. J. Sci. Stat. Comput.— 1986.—7, N 2.—P. 696.

- Barby J. A. et al. Polynomial splines for MOSFET model approximation // IEEE Trans. on Computer-Aided Design.—1988.—7, N 5.—P. 557.

- Люмаров П. П. Применение эрмитовых поликубических интерполяционных сплайнов на криволинейных сетках для электрических моделей МОП-транзисторов с субмикронными размерами // Вычислительные системы, № 137. Приближение сплайнами.—Новосибирск: ИМ СО АН СССР, 1990.

- 4. Merckel G. A simple model of the threshold voltage of short and narrow channel MOSFETs // Solid-State Electron.—1980.—23.—P. 1207.

- Carlson R. E., Fritsch F. N. An algorithm for monotone piecewise bicubic interpolation // SIAM.

J. Numer. Anal.—1989.—26, N 1.—P. 230.

- Груданов Н. Б. Моделирование МДП-транзисторов в режиме слабой инверсии // Автоматизация проектирования в электронике: Республ. межвед. науч.-техн. сб. Киев, 1980. Вып. 21.

- Zangwill W. I. Minimizing a function without calculating derivatives // Computer J.—1967.—10, N 3.—P. 293.

- Merckel G. et al. An accurate large-signal MOS transistor model for use in computer-aided design // IEEE Trans. on Electron. Dev.—1972.—19, N 5.—P. 681.

Поступила в редакцию 28 мая 1991 г.

УДК 621.382.323.001.63:519

П. П. Люмаров

(Новосибирск)

# ПРИМЕНЕНИЕ МОНОТОННЫХ СПЛАЙНОВ ПРИ ПОСТРОЕНИИ МОДЕЛИ МОП-ТРАНЗИСТОРА СО ВСТРОЕННЫМ КАНАЛОМ

Рассмотрено построение моделей MOII-транзистора со встроенным каналом с помощью монотонных интерполяционных сплайнов на адаптивных сетках криволинейной формы.

Введение. Данная работа развивает построение интерполяционных моделей схемного анализа СБИС, начатого в [1], применительно к транзисторам со встроенным каналом (все обозначения [1] будут использоваться без дополнительного пояснения).

Транзистор со встроенным каналом имеет два пороговых напряжения поверхностного и объемного каналов. В связи с существованием экспоненциально убывающих подпороговых токов в измерениях объемное пороговое напряжение условно принимается за напряжение на затворе, при котором ток через транзистор становится меньше  $I_0W/L$ , где  $I_0$  — достаточно малый приведенный пороговый ток, например 0,1 мкА; W и L — ширина и длина канала транзистора. За поверхностное пороговое напряжение в измерениях примем такое напряжение на затворе транзистора, при котором ток на величину  $I_0W/L$  превышает значение на левой границе диапазона измеряемых затворных напряжений. В общем случае в измерениях получают комбинированную пороговую характеристику (назовем ее инверсным пороговым напряжением  $V_{THI}$ ), соответствующую при больших смещениях подложки объемному пороговому напряжению, а при малых — поверхностному.

Использование  $V_{THI}$  в качестве  $V_{TH}$  в уравнении

$$z_{ijk} = \zeta_{\max}((1 + \zeta_k/D_{\zeta})^2 - 1)/((1 + \zeta_{\max}/D_{\zeta})^2 - 1) + V_{TH}(x_i, y_j)$$

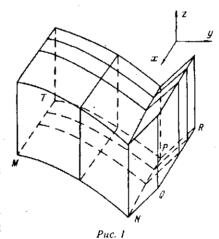

не обеспечивает монотонности преобразования переменных  $(\xi,\eta,\xi)$  в (x,y,z) и всего интерполянта в целом. Применив квадратичную экстраполяцию участков характеристики объемного канала в область поверхностной инверсии, получаем монотонное экстраполированное пороговое напряжение  $V_{THE}$ , пригодное для построения монотонных интерполянтов на криволинейной адаптивной токовой сетке. Функции  $V_{THI}$  и  $V_{THE}$  используются как при построении сплайновой токовой модели, так и в аналитическом расчете зарядовых характеристик (рассмотрение последнего выходит за рамки данной работы). Для интерполянтов этих функций важно не допустить взаимных пересечений, т. е.  $V_{THI} \equiv V_{THE}$  на участке объемных пороговых и  $V_{THI} > V_{THE}$  при появлении поверхностной инверсии канала. Идеализированная пороговая поверхность MNQRPT, полученная с помощью аналитической модели, показана на рис. 1.

При разработке электрических моделей за общую точку обычно выбирается потенциал истока транзистора. В этом случае область рабочих напряжений транзистора задается неравенствами  $0 \le V_{DS} \le V_{ES}, 0 \le V_{GS} \le V_{ES},$   $0 \le V_{GS} \le V_{ES},$  Видно, что при общей подложке появляются два

ограничения: дополнительных  $0 \le V_{DB} \le V_{ES}$  и  $0 \le V_{GS} \le V_{ES}$ . Если их исключить, значения  $V_{DB}$  и  $V_{GB}$  окажутся в пределах:  $0 \le V_{DB} = V_{DS} + V_{SB} \le V_{ES} +$  $+ V_{EB}, \ 0 \le V_{GB} \le V_{ES} + V_{EB}, \ \text{т. e. значи-}$ тельная часть узлов сетки находится за пределами рабочей области транзистора, представляющей собой «усеченный прямоугольник» для пороговой сетки и усеченную криволинейную четырехгранную пирамиду для токовой сетки. За пределами этой рабочей области (в дальнейшем будем называть ее узлы доступными) сеточные напряжения, не выходящие за рамки рабочего диапазона по отношению к истоку, могут превысить значения пробивных напряжений по отношению к подложке и потому исключаются при измерениях, но восполняются при формировании таблиц

сеточных функций алгоритмами монотонной экстраполяции.

При автоматизированных измерениях реально выставленные с фиксированной дискретностью координаты узлов пороговой и токовой сеток не совпадают точно с запрошенными. Кроме того, пороговая сетка по координате x начинается с 0, а измерения пороговых напряжений выполняются лишь при значениях x, обеспечивающих режим насыщения. Если  $I_0 = 0,1$  мкA, то  $x \ge 0,1$  В. В работе предложены алгоритмы многомерной интерполяции, позволяющие ослабить влияние ошибок установки координат узлов, что существенно при малых значениях стоковых и относительных затворных напряжений.

1. Интерполяция пороговых функций  $V_{THI}$  и  $V_{THE}$ . На рис. 1 идеализированное инверсное пороговое напряжение представлено двумя стыкующимися частями поверхности MNPT (объемный канал транзистора) и плоскостью NQPR, параллельной оси x (инверсия на поверхности канала транзистора), с уравнением  $z=y-2\psi_N$ , где  $\psi_N$  — разность потенциалов между серединой запрещенной зоны и уровнем Ферми в полупроводнике в условиях теплового равновесия.

Пороговое напряжение  $V_{THE}$  получается с помощью лагранжевой экстраполяции полиномами 3-го порядка поверхности MNPT под плоскость NQRP. Чтобы гарантировать монотонность экстраполированных данных по обеим переменным, предлагается использовать характеристики, параллельные монотонному одномерному экстраполянту вдоль любой у-линии (например, при  $x = x_2$ ). Обозначив через  $y_i$  самый правый узел объемного порогового напряжения, имсем

$V_{THE}(x_i, y_i) = V_{THE}(x_2, y_i) + V_{THI}(x_i, y_i) - V_{THI}(x_2, y_i)$  для  $y_i < y_j \le 0$ . (1)

Здесь монотонность по x и y обеспечивается соответственно монотонностью  $V_{THI}(x_i, y_i)$  и  $V_{THE}(x_2, y_j)$ .

Рассмотрим функцию  $\Omega(x,y) = V_{THI} - V_{THE}$ , тождественно равную нулю в области объемных пороговых напряжений и монотонно возрастающую на участке поверхностной инверсии. Незначительные нарушения монотонности функций  $V_{THE}$  и  $\Omega$ , вызванные погрешностями измерений, легко устраняются алгоритмами сглаживания. Для каждой функции в отдельности применяется алгоритм расчета производных соответствующего монотонного бикубического сплайна [2]. Функция  $V_{THI}$  и все ее частные производные восстанавливаются из выражения  $V_{THI} = \Omega + V_{THE}$ . Интерполянт  $\Omega$  тождественно равен 0 при  $y \le y_i$  и монотонно возрастает при  $y > y_i$ , в общем виде обеспечивая требуемое соотношение между интерполянтами  $V_{THI}$  и  $V_{THE}$ . Использование локальных базисных бипараболических сплайнов даст совпадение аппроксимантов  $V_{THI}$  и  $V_{THE}$  лишь до значений  $y \le y_i - h_{i-1}/2$ . Кроме того, аппроксимация по точности в регулярных узлах пороговой сетки в среднем на порядок уступает интерполяции. Это сказывается на качестве адаптивной токовой сетки и точности полученного на ней интерполянта.

Пересчет сеточных значений пороговой функции от установленных в измерении координат к значениям с точными координатами узлов сетки выполняется путем многомерной интерполяции по ближайшим соседям. Подробнее этот алгоритм рассмотрен на токовых сетках в следующем разделе.

Если требуемая область узловых напряжений транзистора (с потенциалами относительно истока) приближается к пробивным напряжениям, то набор измеряемых сеточных узлов пороговой сетки ограничивается дополнительным условием  $V_{DB} \leq V_{ES}$ . При формировании пороговой сеточной функции пропущенные во время измерений значения восполняются алгоритмами монотонной экстраполяции. Для этого с помощью интерполяции во всех узлах доступного набора пересчитываются пороговые значения от установленных в измерении координат к координатам узлов сетки и контролируется монотонность пороговой функции  $V_{THI}$  в доступных узлах области объемных порогов и функции  $\Omega$  в области поверхностной инверсии. При необходимости данные сглаживаются в x-направлении линейной функцией по методу наименьших

квадратов или многократным применением сглаживающих локальных базисных кубических сплайнов, точных на линейных функциях. В отличие от параболических последние не гарантируют воспроизведение локальных максимумов в данных и пригодны для восстановления монотонности.

Восполнение недоступных узлов пороговой сетки выполняется вдоль улиний от доступных значений в направлении убывания у по тому же принципу, что и при экстраполяции  $V_{THE}$  с помощью (1). Просмотр начинается от первой линии, содержащей недоступные узлы. Считая, что при  $x=x_{i-1}$  все у-значения уже известны, а  $y=y^*$ — самый левый доступный узел на текущей у-линии (при  $x=x_i$ ), имеем для всех  $y_i < y^*$

$$V_{THI}(x_i, y_i) = V_{THI}(x_{i-1}, y_i) + V_{THI}(x_i, y^*) - V_{THI}(x_{i-1}, y^*).$$

Такое восполнение обеспечивает монотонность сеточных данных по обеим переменным в области объемных порогов.

2. Формирование криволинейной токовой сетки. Так же как и в [3], для транзисторов с индуцированным и встроенным каналами выполняется экстраполяция экспоненциально убывающих подпороговых токов по формуле

$$I_{DS}(x, y, z) = I'_0(x, y) \exp(q(z - V_{THE}(x, y))/(\alpha kT)).$$

(2)

Значение  $I_0'(x,y)$  аппроксимируется с помощью монотонных кубическо-параболических сплайнов на грани  $\zeta=0$  токовой сетки. Отметим, что  $I_0$  на поверхности пороговых напряжений может заметно отличаться от порогового тока  $(I_0W/L)$ , так как при малых значениях x транзистор оказывается в линейной области, где его ток зависит от z и x. У адаптивной криволинейной токовой сетки на грани  $\zeta=0$  всегда имеются отличные от 0 узлы сетки в линейной области работы транзистора.

С учетом подпороговых токов граничные производные  $\Phi'_{\zeta}$  на грани  $\zeta=0$  уже не могут быть приняты равными нулю [1], а рассчитываются с помощью (2).

В случае наличия поверхностного канала возрастание затворного напряжения от  $V_{THE}$  до  $V_{THI}$  практически не сказывается на изменении узловых значений токовой функции (сквозные токи на левом участке затворной характеристики). На этом участке погрешности измерения могут нарушить монотонность токовой функции. Исчезновение поверхностной инверсии при  $z=V_{THI}$  приводит к резкому возрастанию токовой функции с ростом напряжения на затворе, что ухудшает точность интерполяции при z, близких к  $V_{THI}$  (в окрестности излома затворной характеристики). Для обеспечения монотонности сквозной ток F(x, y, z) при  $z < V_{THI}$  составляется из двух слагаемых: постоянного  $F(x, y, V_{THI})$  и экспоненциально убывающего:

$$I(x, y, z) = I_0 W/L \left\{ \exp((z - V_{THI})q/(\alpha kT)) - 1 \right\}.$$

(3)

Если сквозной ток при  $z=V_{THI}\leq (I_0W/L)$ , то он рассматривается как пороговый на участке измерения объемного канала и его экстраполяция в область подпороговых значений осуществляется по формуле (2). Точность интерполяции  $F(x,y,V_{THI})$  в окрестности  $z=V_{THI}$  заметно повышается заменой реальных узловых значений сквозного тока на участке  $z< V_{THI}$  на квадратично-экстраполированные от значений  $F(x,y,z^*)$  до  $I_0W/L$  при  $z=V_{THE}$ , где  $z^*$  первый узсл в направлении z правее  $V_{THI}$ . Это позволяет моделировать близко к реальному излом затворной характеристики ценой разрыва частной производной по z при  $z=V_{THI}(x,y)$ .

Предложенная аппроксимация сквозных токов обеспечивает непрерывность их перехода в подпороговые.

Чтобы с помощью многомерной интерполяции пересчитать значения токовых сеточных функций от установленных в измерении координат к координатам токовой сетки, во время измерений запоминаются не только экспериментальные значения функции, но и реальные координаты узла. Для каждого внутреннего доступного узла сетки выбираются шесть его ближайших пространственных соседей (по расположению в прямоугольной сетке  $(\xi, \eta, \zeta)$ ). Обозначим через  $(x_0, y_0, z_0)$  точные значения координат выбранного узла, а через  $(x_i, y_i, z_i)$ , i = 1, 2, ..., 7, реальные координаты самого выбранного узла и его ближайших соседей. Выберем для интерполяции в окрестности узла  $(x_0, y_0, z_0)$  неполное уравнение второго порядка

$$f(x, y, z) = a_{000} + a_{100}(x - x_0) + a_{200}(x - x_0)^2 + a_{010}(y - y_0) + a_{020}(y - y_0)^2 + a_{001}(z - z_0) + a_{002}(z - z_0)^2.$$

Подставляя в левую часть вместо x, y и z последовательно реальные координаты семи узлов, а в правую часть соответствующие значения функции в этих узлах, получаем линейную систему семи уравнений с семью неизвестными. Найденное из системы значение  $a_{000}$  и будет интерполированным значением функции в узле с точными координатами  $(x_0, y_0, z_0)$ .

Для узлов, лежащих на границе сетки, исключая границу, совпадающую с пороговыми напряжениями, соседи выбираются только среди доступных ближайших. При этом вдоль направления, перпендикулярного границе, степень интерполянта понижается до 1. Использование для этой цели квадратичной интерполяции с привлечением более далеких внутренних узлов, как правило, ухудшает точность. Привлечение диагональных ближайших соседей с одновременным добавлением в уравнение перекрестных членов типа ху, хх или ух не отражается на повышении точности интерполяции.

Поведение токовой функции в окрестности границы  $\xi=0$  определяется экспонентой (2), а сами значения токов в узлах этой грани на 1-3 порядка меньше значений во внутренних узлах сетки. Поэтому вместо интерполяции с использованием ближайшего соседа в направлении z выполняется экспоненциальная экстраполяция.

Рабочая область напряжений токовой сетки при отсчете потенциалов от подложки представляет собой усеченную четырехгранную пирамиду. Восполнение информации в недоступных узлах параллелепипеда криволинейной токовой сетки удобнее всего выполнять вдоль линий уровня, присваивая всем недоступным узлам текущей линии у значение самого левого доступного узла.

3. Возможности новых моделей при проектировании схем и некоторые результаты. В схемном проектировании модель должна не только точно воспроизводить вольт-амперные и емкостные характеристики при заданном наборе электрофизических и топологических параметров, но и предсказывать поведение этих характеристик при разбросе электрофизических параметров, в частности, учитывать разброс подвижности и пороговых напряжений, влияние геометрии и температурную зависимость характеристик.

Влияние геометрии в нулевом приближении учитывается с помощью коэффициента  $(W/L)/(W_0/L_0)$ , где индексом 0 помечены параметры, установленные при измерении токовых сеточных данных. Более точно учесть геометрические размеры можно введением размерных зависимостей, как в [4]. Разброс подвижности учитывается множителем (первоначально установленным

в единицу), а разброс пороговых напряжений — дополнительным аддитивным

слагаемым (первоначально установленным в нуль), сдвигающим всю поверхность пороговых напряжений  $V_{2H}(x,y)$ . Температурная зависимость характеристик учитывается с помощью аналитического расчета поправочного множителя к коэффициенту подвижности и дополнительного слагаемого к пороговому напряжению.

В качестве входных данных для интерполяционных моделей, результаты моделирования которых представлены на рис. 2—4, использовалась аналитическая модель со встроенным каналом [5]. Это позволило при оценке точности различных алгоритмов интерполяции исключить влияние случайных погрешностей, связанных с измерениями.

Использование при построении криволинейной области интерполяции непосредственно измеряемого порогового напряжения  $V_{THI}$  приводит к тому, что

на характеристиках подложки появляются ложные пульсации, вызванные резким изменением в характере поведсния порогового напряжения в момент появления поверхностной инверсии канала. На рис. 2 представлены подложечные характеристики, соответствующие аналитической модели в качестве

| *** |   | ~ |   |   |   |   |  |

|-----|---|---|---|---|---|---|--|

| T   | a | Ö | Л | И | П | а |  |

| Тип<br>оціибки | Транзі | истор с индуц | ированным к | аналом | Трянзистор со встроенным каналом |        |        |        |

|----------------|--------|---------------|-------------|--------|----------------------------------|--------|--------|--------|

| Сетка          | 3 × 5  | 3 × 10        | 4 × 18      | 5 × 28 | 3 × 5                            | 3 × 10 | 4 × 18 | 5 × 28 |

| $A_e$          | 0,008  | 0,001         | 0,0002      | 1000,0 | 0,680                            | 0,253  | 0,148  | 0,132  |

| $R_e$          | 0,576  | 0,063         | 0,018       | 0,0051 | 5,61                             | 1,99   | 1,18   | 1.04   |

|                       |       | <u></u> ,          | Т                       | абли  | ца 2  |

|-----------------------|-------|--------------------|-------------------------|-------|-------|

| Cette 2 x y x z       | Me, % | R <sub>e</sub> , % | Сегках хухг             | Me. % | Re. % |

| 5 × 3 × 6             | 1,05  | 2,49               | 9 × 3 × 10              | 0,99  | 3,67  |

| $7 \times 3 \times 9$ | 0,89  | 3,38               | $18 \times 3 \times 18$ | 0,98  | 2,83  |

оригинала (сплошная линия) и двум интерполяционным транзисторам с сетками:  $6 \times 20$ -пороговой и  $5 \times 6 \times 13$ -токовой (штрихпунктирная кривая);  $8 \times 9$ -пороговой и  $8 \times 9 \times 20$ -токовой (штриховая). Вертикальные прерывистые линии на рис. 2, 4 указывают правую и левую границы токовой сетки по напряжению подложки. Наиболее значительные пульсации наблюдаются при несовпадении пороговой и токовой сеток по х- и у-координатам (штрихпунктирная кривая).

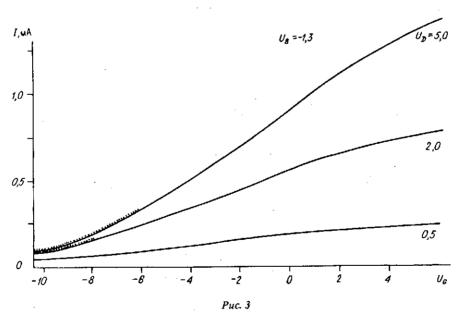

На рис. 3, 4 представлены характеристики, соответствующие аналитической модели в качестве оригинала (сплошная кривая) и трем интерполяционным транзисторам с сетками:  $6 \times 20$ -пороговой и  $4 \times 5 \times 9$ -токовой (точки);  $6 \times 20$ -пороговой и  $5 \times 6 \times 13$ -токовой (штрихпунктирная кривая);  $6 \times 20$ -пороговой и  $8 \times 9 \times 20$ -токовой (штриховая).

При построении областей интерполяции для этих транзисторов использовались монотонные экстраполированные пороговые напряжения  $V_{THE}$ . Приведенные на рисунках характеристики охватывают всю активную область транзистора со встроенным каналом. При этом достигается высокая точность интерполяции даже при возникновении поверхностной инверсии канала (остаточные токи слева на рис. 3). Характеристики транзистора с токовой сеткой  $8 \times 9 \times 20$  практически всюду совпадают с оригиналом.

В таблицах приняты те же обозначения, что и в [1]. Точность интерполяции оценивалась статистическим методом.

В табл. 1 приведены ошибки интерполяции пороговых напряжений.

На практике часто напряжение на затворе транзистора со встроенным каналом изменяется лишь в области неотрицательных значений. В этом случае участок отрицательных напряжений на затворе (от  $V_{THE}$  и до 0), соответствующий характеристикам с наибольшей кривизной, может быть перекрыт одним большим шагом интерполяции, на котором не требустся высокая точность. Это позволяет сократить число узлов как по x-, так и по z-координатам при сохранении высокой точности интерполяции (табл. 2).

Заключение. Предложены алгоритмы интерполяционной модели МОПтранзистора со встроенным каналом.

Алгоритмы внедрены в электрические модели пакета ехемотехнического проектирования и хорошо зарекомендовали себя в качестве универсального инструмента схемного моделирования. По точности они в 10 раз превосходят малоразмерные аналитические с подогнанными под экспериментальные данные параметрами.

## СПИСОК ЛИТЕРАТУРЫ

1. Люмаров П. П. Монотонные сплайны на адаптивных сетках трех переменных для электрических МОП-моделей // Автометрия.—1992.—№ 3.

- Carlson R. E., Fritsch F. N. An algorithm for monotone piecewise bicubic interpolation // SIAM J. Numer. Anal.—1989.—26, N 1.—P. 230.

- 3. Shima T. et al. Three-dimensional table look-up MOSFET-model for precise circuit simulation // IEEE J. of Solid State Circuits.—1982.—17, N 3.—P. 449.

- 4. Hsu M. C. et al. Inverse-geometry dependence of MOS transistor electrical parameters // IEEE Trans. on Computer-Aided Design.—1987.—6, N 4.—P. 582.

- 5. Груданов Н. Б. и др. Модель МДП-транзистора со встроенным каналом // Автоматизация проектирования в электронике: Респ. межвед. науч.-техн. сб.—Киев, 1980.—Вып. 21.

Поступила в редакцию 28 мая 1991 г.

УДК 681.327

### А. И. Мишин

(Новосибирск)

# ПАМЯТЬ С АДРЕСАЦИЕЙ ПО СОДЕРЖАНИЮ И ЕЕ ПОТЕНЦИАЛЬНЫЕ ВОЗМОЖНОСТИ

Проводится сравнительный анализ параллельного и последовательного поисков на точное соответствие. Дается оценка трудоемкости поиска при использовании ассоциативного кодирования (хеширования), основанная на r-разрядных обращениях к запоминающему устройству с произвольной выборкой (ЗУПВ) (1 < r < m, m — число разрядов в слове). Показано, что минимальное среднее число обращений к памяти, равное 1, достигается при двухкратной избыточности памяти и r = 4. Показано, что минимальное среднее время поиска достигается не параллельным поиском в ассоциативной памяти (АЗУ), а при использовании метода хеширования, реализуемого памятью с адресацией по содержанию (ПАС), включающей ЗУПВ и процессор. Сравнение поиска в АЗУ и ПАС по комплексному критерию  $\eta$ , определяемому произведением площади  $\Pi$ , занимаемой памятью емкостью M (слов), на время поиска T, дает  $\eta = (\Pi T)$ Азу/ $(\Pi T)$ зупв =  $O(M^{3/4})$ , причем время поиска в АЗУ в  $O(M^{4/3})$  раз больше, чем в ЗУПВ.

Введение. Известно, что возможность адресации по содержанию существенно повышает производительность ЭВМ за счет более эффективной организации поиска данных. Однако несмотря на то что основные принципы адресации по содержанию были разработаны более 30 лет назад, ассоциативное запоминающее устройство используется лишь в качестве буферной памяти небольшой емкости. Основным недостатком АЗУ является неэффективное исполнение операции поиска на точное соответствие. При исполнении этой операции каждый элемент АЗУ выполняет проверку на точное соответствие предъявленного слова и слова, хранящегося в самом элементе, т. е. все элементы работают одновременно. Однако параллельный поиск на точное соответствие не ускоряет процесса поиска по сравнению с поиском в однопроцессорной ЭВМ с памятью произвольного доступа. Понятие «ассоциативный» отражает лишь факт наличия связи между данными и не имеет отношения к самому механизму поиска информации. Поэтому вычислительному устройству, ориентированному на решение задачи поиска информации, в большей степени подходит название память с адресацией по содержанию. В литературе также используется термин «память с адресацией по данным».

Выборка и запись информации в запоминающие ячейки ПАС проводятся в зависимости от содержащихся в них данных. Не имеет принципиального значения, каким способом ведется поиск: программным путем (как в ЭВМ) или с помощью параллельного опроса (как в АЗУ).

Используя ПАС, можно, в частности, получить ответы на следующих два вопроса: 1) принадлежит ли некоторое слово w множеству данных (проверка на точное соответствие); 2) для заданного слова w найти во множестве данных слово w', наиболее близкое к w (поиск на наилучшее соответствие).